随着人工智能应用的爆发式增长,AI芯片作为算力的核心载体,其发展路径与挑战日益成为业界焦点。当前,AI芯片正面临两类关键瓶颈,同时呈现出三大发展趋势,而存储技术的创新则有望开拓性能提升的新疆界。

两类瓶颈:算力与能效的挑战

- 算力墙与内存墙:

- 算力墙:随着模型参数量的指数级增长(如千亿、万亿参数模型),对芯片峰值算力(TOPS)的需求已逼近物理极限。传统架构下,单纯堆砌计算单元带来的收益递减,且芯片面积、功耗和成本急剧上升。

- 内存墙:数据在存储单元与计算单元之间的搬运成为主要性能瓶颈。频繁的数据移动导致高延迟与高能耗,尤其在处理大规模矩阵运算时,内存带宽不足严重制约了算力的有效利用,形成“存储制约计算”的困境。

- 能效墙与通用性困境:

- 能效墙:AI训练与推理的能耗日益惊人。在追求更高性能的如何降低每瓦特算力的能耗(即提升能效比)是芯片设计的关键挑战,直接影响部署成本与可行性(如边缘设备、数据中心)。

- 通用性与灵活性的平衡:专用芯片(ASIC)针对特定算法(如Transformer)效率极高,但难以适应快速演化的AI模型;通用芯片(如GPU)灵活性好,但往往在能效上做出妥协。如何实现动态可重构、软硬件协同的架构成为难点。

三大趋势:架构创新与生态演进

- 架构多元化与异构计算:

- 从传统的CPU、GPU主导,走向CPU+GPU+XPU的异构融合。专用领域架构(DSA)针对AI负载优化,如TPU、NPU等;神经拟态芯片、光计算芯片等非冯·诺依曼架构也在探索中,旨在模拟人脑的高效计算模式。

- Chiplet(芯粒)与先进封装:通过将大芯片拆分为多个小芯粒,采用2.5D/3D封装集成,提升良率、降低设计成本,并实现内存与计算单元的近距离互连,缓解内存墙问题。

- 软件定义硬件与编译优化:

- 硬件不再孤立发展,而是与编译器、框架深度耦合。AI编译技术(如MLIR、TVM)通过对计算图进行优化、调度与代码生成,使同一硬件能高效支持多样化的模型,提升通用性。

- 开源指令集(如RISC-V)与开放芯片生态正在降低设计门槛,推动定制化AI芯片的繁荣。

- 场景化与全栈优化:

- 芯片设计日益贴近终端场景:云端训练芯片追求极致算力与精度;边缘推理芯片注重低功耗、实时性;终端设备则强调整合度与成本。

- “存储-计算-通信”协同设计:从单一算力指标转向全栈优化,包括内存层次设计、片间互联技术(如NVLink、CXL)及集群网络,以提升系统整体效率。

存储技术:开拓性能新疆界的关键

存储技术的创新正成为打破AI芯片瓶颈的核心突破口:

- 存算一体(Computing-in-Memory):

- 将计算单元嵌入存储阵列中,直接在数据存储位置进行处理,极大减少数据搬运。基于SRAM、DRAM或新兴非易失存储器(如ReRAM、PCM)的存算一体芯片,已在边缘推理场景展示出数量级的能效提升潜力。

- 高带宽内存(HBM)与先进封装:

- HBM通过硅通孔(TSV)技术将DRAM堆叠在逻辑芯片上,提供远超GDDR的带宽(如HBM3带宽可达819GB/s以上)。结合CoWoS等2.5D/3D封装,实现了“内存紧贴计算”,有效缓解带宽瓶颈。

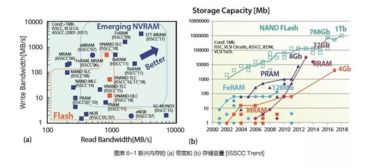

- 新型非易失存储器与近存计算:

- ReRAM(阻变存储器)、MRAM(磁阻存储器)等兼具高速、低功耗、高密度特性,不仅可用于存算一体,也可构建高速缓存或持久内存层,优化数据存取路径。

- 近存计算将计算单元置于内存芯片附近,作为存算一体的过渡方案,已在部分AI加速器中应用。

- 存储层级智能化:

- 通过硬件与系统软件协同,动态管理数据在各级存储(如HBM、DDR、NVMe SSD)间的分布,预测数据访问模式,实现数据预取与缓存优化,最大化内存带宽利用率。

###

AI芯片的竞赛已从单纯算力比拼,进入架构创新、能效决胜、软硬协同的深水区。两类瓶颈(算力/内存墙、能效/通用性)倒逼技术变革,三大趋势(异构融合、软件定义、场景化)指引发展方向。而存储技术的突破——尤其是存算一体与先进封装——正为AI芯片开拓出新的性能疆界,有望在未来几年内催生出更高效、更灵活的算力基石,赋能千行百业的智能化升级。技术开发者需密切关注这些交叉领域的进展,在算法、硬件与系统的协同优化中寻找创新机会。